# Section 46. Scalable Comparator Module

# HIGHLIGHTS

This section of the manual contains the following major topics:

| 46.1  | Introduction                           |       |

|-------|----------------------------------------|-------|

| 46.2  | Control Register                       |       |

| 46.3  | Comparator Operation                   |       |

| 46.4  | Comparator Response Time               |       |

| 46.5  | Comparator Outputs                     |       |

| 46.6  | Analog Input Connection Considerations |       |

| 46.7  | Comparator Interrupts                  |       |

|       | Code Examples                          |       |

| 46.9  | Operation During Sleep and Idle Modes  |       |

| 46.10 | Effects of a Reset                     |       |

| 46.11 | Related Application Notes              | 46-13 |

| 46.12 | Revision History                       |       |

### 46.1 INTRODUCTION

The scalable comparator module is comprised of several identical analog comparator blocks, each complete with its own supporting input selectors and output logic. Each comparator can be configured in a variety of ways, independent of the other comparators. Inputs can be selected from four analog inputs multiplexed with I/O pins, external voltage references, and the on-chip voltage reference (see **Section 20. "Comparator Voltage Reference Module**") or the on-chip band gap reference. A status register provides a single location to monitor all comparators simultaneously.

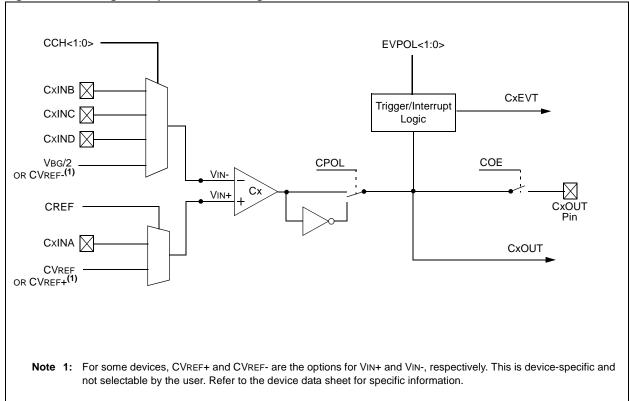

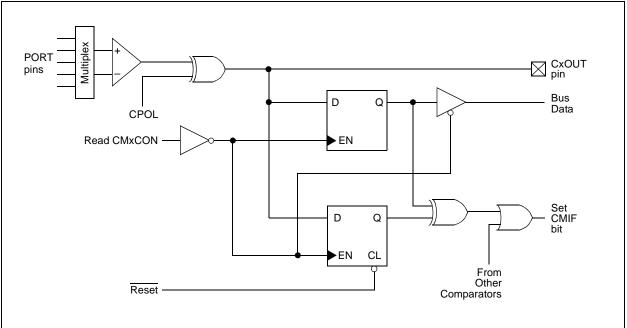

The block diagram for a single comparator is shown in Figure 46-1. Depending on the device family, the scalable comparator module may contain anywhere from two to six analog comparators; the most commonly used configuration contains three. Refer to the device data sheet for specific information.

**Note:** A comparator module with two analog comparators may also be the integrated dual comparator module, described in the Family Reference Manual chapter "**Dual Comparator Module**" (DS39710). Check the device data sheet to verify which comparator module is included in a particular device.

Figure 46-1: Single Comparator Block Diagram

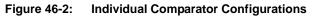

# 46.1.1 Comparator Configuration

Each of the several comparators has complete control over its input selections, output inversion, output on I/O pin and event generation. The VIN- input of each comparator can select from one of three I/O pins (CxINB, CXINC or CXIND), while the VIN+ input of the comparator comes from the comparator voltage reference, or the positive I/O pin (CxINA or CVREF). The comparators provide a common-mode voltage range which is nominally rail-to-rail, VSS to VDD. Refer to the particular data sheet for actual electrical specifications. The configuration options are shown in Figure 46-2.

The comparator also has four options to configure a separate event/trigger output based on changes of the comparator's output. Users can select from rising-edge, falling-edge, and all transitions.

If the Comparator mode is changed, the comparator output level may not be valid for the specified mode change delay.

**Note:** Comparator interrupts should be disabled during a Comparator mode change; otherwise, a false interrupt may occur.

© 2010 Microchip Technology Inc.

## 46.2 CONTROL REGISTER

The scalable comparator module uses several registers for configuration and control. Depending on the number of comparators, up to seven registers are implemented.

The CMxCON registers (Register 46-1) are used to configure the individual comparators. Each comparator uses its own individually-numbered CMCON register. The CON bit (CMxCON<15>) enables or disables the individual comparator. The COE bit (CMxCON<14>) enables the output of the comparator to appear on the corresponding CxOUT pin. The COUT bit (CMxCON<8>) reports the output state of the comparator, as determined by the relative values of Vin+ and Vin- and the CPOL bit (CMxCON<13>).

The CREF and CCH<1:0> bits (CMxCON<4> and <1:0>, respectively) configure the VIN+ and VIN- inputs to the comparator. The VIN+ pin can select from a dedicated analog input (CxINA) or the comparator voltage reference (CVREF or CVREF+). The VIN- pin can select from four sources: three other dedicated analog inputs (CxINB, CxINC or CxIND) or voltage reference (CVREF- or VBG/2). Taken together, this provides a total of eight input configurations for each comparator. (The CVREF and internal band gap options available to the user are solely determined by the comparator voltage reference module available on the microcontroller. Voltage reference options are controlled by the CVRCON register, discussed in **Section 20. "Comparator Voltage Reference Module"**.)

The EVPOL bits (CMxCON<7:6>) configure the event-detection logic to report changes to the output state of the comparator, which can in turn be used for event or interrupt generation. The options include event generation on rising state changes (low-to-high), falling state changes (high-to-low), and all state changes. When a configured event occurs, it is flagged by the CEVT bit (CMxCON<9>).

The CMSTAT register (Figure 46-2) serves as a convenient monitor for the status of all comparators; one CMSTAT register is implemented for the entire module. The CxOUT and CxEVT bits mirror the states of the corresponding bits in the CMxCON registers on a synchronous basis. In the CMSTAT register, all CxOUT and CxEVT bits are read-only, and cannot be changed. In addition, the CMIDL bit (CMSTAT<15>) determines how the comparator module as a whole operates when the microcontroller is in Idle mode.

| Register 46-1:  | CMxCON:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Comparator x                                            | Control Regi           | sters (Compa     | rators 1 Thro   | ugh n)            |                |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------------|------------------|-----------------|-------------------|----------------|--|--|--|

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0                                                   | U-0                    | U-0              | U-0             | R/W-0             | R-0            |  |  |  |

| CON             | COE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CPOL                                                    | —                      | _                | —               | CEVT              | COUT           |  |  |  |

| bit 15          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                         |                        |                  |                 |                   | bit 8          |  |  |  |

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | U-0                                                     | R/W-0                  | U-0              | U-0             | R/W-0             | R/W-0          |  |  |  |

| EVPOL1          | EVPOL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                       | CREF                   |                  |                 | CCH1              | CCH0           |  |  |  |

| bit 7           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                         | OREI                   |                  |                 | Con               | bit (          |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                         |                        |                  |                 |                   |                |  |  |  |

| Legend:         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                         |                        |                  |                 |                   |                |  |  |  |

| R = Readable    | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | W = Writable I                                          | bit                    | U = Unimpler     | nented bit, rea | ad as '0'         |                |  |  |  |

| -n = Value at P | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | '1' = Bit is set                                        |                        | '0' = Bit is cle | ared            | x = Bit is unkn   | iown           |  |  |  |

|                 | 1 = Compara                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | rator Enable bit<br>ator is enabled<br>ator is disabled | t                      |                  |                 |                   |                |  |  |  |

|                 | <b>COE:</b> Comparator Output Enable bit<br>1 = Comparator output is present on the CxOUT pin<br>0 = Comparator output is internal only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                         |                        |                  |                 |                   |                |  |  |  |

|                 | 1 = Compara                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | earator Output F<br>ator output is inv                  | /erted                 | bit              |                 |                   |                |  |  |  |

|                 | 0 = Comparator output is not inverted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                         |                        |                  |                 |                   |                |  |  |  |

|                 | Unimplemented: Read as '0'<br>CEVT: Comparator Event bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                         |                        |                  |                 |                   |                |  |  |  |

|                 | 1 = Compara<br>disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                         | ed by EVPOL·<br>leared | <1:0> has occu   | ırred; subseqı  | uent triggers and | interrupts are |  |  |  |

| bit 8           | COUT: Comp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | arator Output b                                         | it                     |                  |                 |                   |                |  |  |  |

|                 | When $CPOL = 0$ :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                         |                        |                  |                 |                   |                |  |  |  |

|                 | 1 = VIN + > VIN -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                         |                        |                  |                 |                   |                |  |  |  |

|                 | 0 = VIN + < VIN - VIN |                                                         |                        |                  |                 |                   |                |  |  |  |

|                 | When CPOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                         |                        |                  |                 |                   |                |  |  |  |

|                 | 1 = VIN + < VIII = VIII + > VIII = VIII + > VIII = VIIII + > VIIII = VIIII = VIIII + > VIIII = VIIII = VIIII = VIIII = VIIII = VIIIII = VIIII = VIIIII = VIIII = VIIIII = VIIII = VIIIII = VIIIII = VIIIII = VIIIII = VIIIII = VIIII = VIIII = VIIII = VIIIII = VIIIIIIII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                         |                        |                  |                 |                   |                |  |  |  |

| bit 7-6         | <b>EVPOL&lt;1:0&gt;:</b> Trigger/Event/Interrupt Polarity Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                         |                        |                  |                 |                   |                |  |  |  |

|                 | 11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                         |                        |                  |                 |                   |                |  |  |  |

|                 | 10 = Trigger/event/interrupt generated on transition of the comparator output:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                         |                        |                  |                 |                   |                |  |  |  |

|                 | If CPOL = 0 (non-inverted polarity):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                         |                        |                  |                 |                   |                |  |  |  |

|                 | High-to-low transition only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                         |                        |                  |                 |                   |                |  |  |  |

|                 | If CPOL = 1 (inverted polarity):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                         |                        |                  |                 |                   |                |  |  |  |

|                 | Low-to-high transition only.<br>01 = Trigger/Event/Interrupt generated on transition of comparator output:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                         |                        |                  |                 |                   |                |  |  |  |

|                 | If $CPOL = 0$ (non-inverted polarity):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                         |                        |                  |                 |                   |                |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | high transition                                         |                        |                  |                 |                   |                |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | L = 1 (inverted )                                       | -                      |                  |                 |                   |                |  |  |  |